# Quo Vadis, SLD? Reasoning About the Trends and Challenges of System Level Design

Recognizing common requirements for co-design of hardware and software in diverse systems may lead to productivity gains, lower costs and first-pass design success.

By Alberto Sangiovanni-Vincentelli, Fellow IEEE

ABSTRACT | System-level design (SLD) is considered by many as the next frontier in electronic design automation (EDA). SLD means many things to different people since there is no wide agreement on a definition of the term. Academia, designers, and EDA experts have taken different avenues to attack the problem, for the most part springing from the basis of traditional EDA and trying to raise the level of abstraction at which integrated circuit designs are captured, analyzed, and synthesized from. However, my opinion is that this is just the tip of the iceberg of a much bigger problem that is common to all system industry. In particular, I believe that notwithstanding the obvious differences in the vertical industrial segments (for example, consumer, automotive, computing, and communication), there is a common underlying basis that can be explored. This basis may yield a novel EDA industry and even a novel engineering field that could bring substantial productivity gains not only to the semiconductor industry but to all system industries including industrial and automotive, communication and computing, avionics and building automation, space and agriculture, and health and security, in short, a real technical renaissance.

Manuscript received May 13, 2006; revised December 7, 2006. This work was supported in part by the Gigascale System Research Center, the Center for Hybrid and Embedded Software Systems (CHESS) at the University of California, Berkeley, which receives support from the National Science Foundation (NSF award CCR-0225610), the State of California Micro Program, and the following companies: Agilent, Bosch, DGIST, General Motors, Hewlett Packard, Infineon, Microsoft, National Instruments, and Toyota, This work was also supported by the European Project SPEEDS and the Networks of Excellence Artist2 and Hycon. The author is with the Department of Electrical Engineering and Computer Science, University of California, Berkeley, CA 94720 USA (e-mail: alberto@eecs.berkeley.edu).

Digital Object Identifier: 10.1109/JPROC.2006.890107

In this paper, I present the challenges faced by industry in system level design. Then, I propose a design methodology, platform-based design (PBD), that has the potential of addressing these challenges in a unified way. Further, I place methodology and tools available today in the PBD framework and present a tool environment, Metropolis, that supports PBD and that can be used to integrate available tools and methods together with two examples of its application to separate industrial domains.

KEYWORDS | Embedded software; embedded systems; models and tools; platform-based design (PBD); system-level design (SLD); system-level design environments

## I. INTRODUCTION

Electronic design automation (EDA) has played a pivotal role in the past 25 years in making it possible to develop a new generation of electronic systems and circuits. However, innovation in design tools has slowed down significantly as we approach a limit in the complexity of systems we can design today satisfying increasing constraints on time-tomarket and correctness. The EDA community has not succeeded as of today in establishing a new layer of abstraction universally agreed upon that could provide productivity gains similar to the ones of the traditional design flow (Register Transfer Level (RTL) to GDSII) when it was first introduced. Nor has it been able to expand significantly into new adjacent markets to increase its total available market. Among the adjacencies of interest, I believe the electronics system market has great potential since system companies that are now facing significant

difficulties due to an exponentially raising complexity and to increased demands on functionality, correctness, and time-to-market are contemplating a radical change in the way they bring new products to market.

In this paper, I will discuss the following two aspects.

- Raising the level of abstraction when designing chips. In this framework, the term system-level design for an integrated circuit relates to any level of abstraction that is "above" RTL. Transaction level modeling (TLM), behavioral, algorithmic, and functional modeling are terms often used to indicate higher levels of abstraction in hardware design. The International Technology Roadmap for Semiconductors (ITRS) in 2004 places SLD "a level above RTL including both HW and SW design." SLD is defined to "consist of a behavioral (before HW/SW partitioning) and architectural level (after)" and is claimed to increase productivity by 200K gates/designer-year. The ITRS states that SLD will produce an estimated 60% productivity improvement over what they call the "intelligent testbench" approach (the previously proposed electronic system design improvement) [178]. While these claims cannot be verified as yet and do look quite aggressive, most agree that the overarching benefits that ESL should bring to the table are to:

- a) raise the level of abstraction at which designers express systems;

- enable new levels of design reuse.

- Dealing with electronics system design and, in particular, embedded system design. In the context of this paper, the term embedded systems refers to the electronic components (which almost always include one or more software programmable parts) of a wide variety of personal or broad-use devices, e.g., a mechanical system such as an automobile, a train, a plane, an electrical system such as an electrical motor or generator, a chemical system such as a distillation plant, or health-care equipment such as a pacemaker. Hence, an embedded system is a special-purpose system in which the computing element is completely encapsulated by the device it controls. Unlike a general-purpose computer, an embedded system performs one or a few predefined tasks, usually with very specific requirements [204]. In technical terms, an embedded system interacts with the surrounding environment in a controlled way satisfying a set of requirements on responsiveness in terms of quality and timeliness. Typically, it has to satisfy implementation requirements such as cost, power consumed, and use of limited physical resources. Ideally, its interaction with the environment should be continuously available for the entire life of the artifact.

To deal with system-level problems, let them be at the chip or embedded system level, the issue to address is not developing new tools, albeit they are essential to advance the state of the art in design, rather, it is the understanding of the principles of system design, the necessary change to design methodologies, and the dynamics of the supply chain. Developing this understanding is necessary to define a sound approach to the needs of the system and IC companies as they try to serve their customers better, to develop their products faster and with higher quality. It is no wonder that EDA experts have stayed away from system-level design; in fact, EDA experts are essentially tied to the semiconductor industry needs in the implementation flow with little or no expertise in the intricacies of embedded systems that include a large amount of software and system integration concerns. The motivation for EDA experts to learn system design has not been there as yet since:

- IC companies are still struggling with the under-1) standing of higher levels of abstraction;

- system companies have not perceived as yet design methodology or tools to be on their critical path, hence they have not been willing to invest in "expensive" tools.

Clearly, as we are hitting a wall in the development of the next generation systems, this situation is rapidly changing. Major productivity gains are needed and better verification and validation is a necessity as the safety and reliability requirements of embedded systems become more stringent and the complexity of chips is hitting an all-time high. Several approaches have emerged in the design community to improve the situation and some EDA companies have invested in the area but a broad EDA industry support for these approaches is still missing.

I share with a number of colleagues [111], [112], [131], [135], [176], [188], [208] (this list also provides an excellent set of references for the state-of-the-art and directions for embedded system design) the strong belief that a new design science must be developed to address the challenges listed above where the physical is married to the abstract, where the world of analog signals is coupled with the one of digital processors, and where ubiquitous sensing and actuation make our entire environment safer and more responsive to our needs. SLD should be based on the new design science to address our needs in a fundamental way. However, the present directions are not completely clear as the new paradigm has not yet fully emerged in the design community with the strength necessary to change the EDA and design technology landscape, albeit the papers quoted in this paragraph have chartered the field with increasing clarity.

Support for the development of this design science is given in the U.S. by the traditional research funding organizations in collaboration with industrial associations. The Gigascale System Research Center (GSRC) [101] of the MARCO program [a joint initiative of the Defense

Advanced Research Project Agency (DARPA) and the Semiconductor Industry Association (SIA)] and the National Science Foundation (NSF) with the Center for Hybrid and Embedded Software Systems (CHESS) [112] are two examples of this effort. However, a much stronger effort is afoot in Europe, where the European community has been supporting embedded system research and novel methodologies for chip design for years with large integrated projects (e.g., SPEEDS) and networks of excellence (e.g., Artist 2 [2] and HYCON [119]) and is planning an increased effort for the VII Framework. In addition, a technology platform, Artemis [51], was formed three years ago by the leading European industrial companies (the initial founding group included Nokia, Ericsson, ST, ABB, Airbus, Infineon, British Telecom, Siemens, Bosch, Contiteves, Daimler-Chrysler, Thales, FIAT, Finmeccanica, Philips, COMAU, Symbian, Telenor, and PARADES with the support of research organizations such as IMEC, Verimag, and the Technical University of Vienna, a healthy combination of Academia, service providers, software companies, system, subsystem and semiconductor manufacturers). The companies have recently formed the Artemis Industrial Association (ARTEMISIA), while the European community is deciding to make it a joint technology initiative, an instrument to funnel substantial resources of the member states. In the last meeting of the European Community Prime Ministers on October 2006, Artemis was quoted by some of the participants (in particular, the Finnish Prime Minister) as an example of agenda setting initiative for the industrial future of Europe.

This paper is not intended to review exhaustively the various approaches and tools that have been proposed over the years (a reader interested in tools and environments available today is referred to [63] for a taxonomy), albeit I will review the most relevant contributions in the perspective presented here.

The paper is organized as follows: in Section II, I focus on the pressing concerns of system level design together with the strategic and business concerns in the supply chains of the mobile terminal and automotive vertical domains as examples of the issues to be taken into consideration when we think about expanding the reach of design methodology and tools. I then present my view on how to form a unified approach to embedded system design, platform-based design (PBD), that could provide a solution to the challenges presented in the previous sections (Section III). In Section IV, I describe some of the most promising approaches to embedded system design using the PBD context as a guide. Then, I present a brief overview of a system design framework that supports this methodology (Section V) and that could form the basis for a unified environment for system level design and integration. In this section, I also present two test cases of the application of the methodology and of the framework from widely different industrial domains: the design of a JPEG encoder on a heterogeneous single chip computing platform and the design of a distributed architecture for supervisory control in automotive. In Section VI, I draw conclusions and indicate future directions for research and industrial developments.

Notably missing from this paper is testing. The topic is extremely important for SLD but to do justice to it, an entire new paper would be needed.

## II. SETTING THE STAGE: CHALLENGES OF SYSTEM LEVEL DESIGN

In the present technology environment and industrial structure, SLD has to address concerns of individual players in the industrial domain that are facing serious problems in bringing their products to market in time and with the required functionality. I do believe that SLD also needs to be concerned about the entire industrial supply chain that spans from customer-facing companies to subsystem and component suppliers, since the health of an industrial sector depends on the smooth interaction among the players of the chain as if they were part of the same company. In this section, I present a view on both challenges that underline commonalities that allow a unified approach to SLD.

#### A. Managing Complexity and Integration

The ability to integrate an exponentially rising number of transistors within a chip, the ever-expanding use of electronic embedded systems to control increasingly many aspects of the "real world," and the trend to interconnect more and more such systems (often from different manufacturers) into a global network are creating a challenging scenario for embedded system designers. Complexity and scope are exploding into the three interrelated but independently growing directions, while teams are even shrinking in size to further reduce costs. In this scenario, the three challenges that are taking center stage are as follows.

1) Heterogeneity and Complexity of the Hardware Platform: The trends mentioned above result in exponential complexity growth of the features that can be implemented in hardware. The integration capabilities make it possible to build a real complex system on a chip including analog and RF components, general purpose processors (GPP) and Application-Specific Instruction-set Processors (ASIP). The decision of what goes on a chip is no longer dictated by the amount of circuitry that can be placed there, but by reliability, yield, power consumption, performance, and ultimately cost (it is well known that analog and RF components force the use of more conservative manufacturing lines with more processing steps than pure digital ICs). Even if manufacturing concerns suggest to implement hardware in separate chips, the resulting package may still be very small given

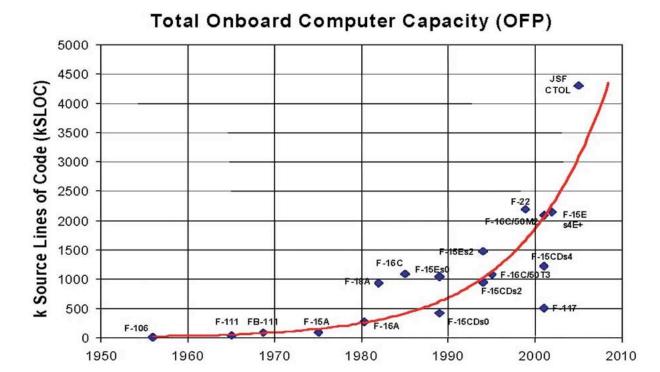

#### Fig. 1. Software growth in avionics.

the advances in packaging technology yielding the concept of system-in-package (SiP). Pure digital chips are also featuring an increasing number of components. Design time, cost, and manufacturing unpredictability for deep submicron technology make the use of custom hardware implementations appealing only for products that are addressing a very large market and for experienced and financially rich companies. Even for these companies, the present design methodologies are not yielding the necessary productivity forcing them to increase beyond reason the size of design and verification teams. These IC companies (for example Intel, Freescale, ST, and TI) are looking increasingly to system design methods to allow them to assemble large chips out of predesigned components and to reduce validation costs (design reuse). In this context, the adoption of design models above RTL and of communication mechanism among components with guaranteed properties and standard interfaces is only a matter of time.

2) Embedded Software Complexity: Given the cost and risks associated to developing hardware solutions, an increasing number of companies is selecting hardware platforms that can be customized by reconfiguration and/ or by software programmability. In particular, software is taking the lion's share of the implementation budgets and cost. In cell phones, more than 1 million lines of code is standard today, while in automobiles the estimated number of lines by 2010 is in the order of hundreds of millions [199]. The number of lines of source code of embedded software required for defense avionics systems is also growing exponentially as reported in Fig. 1 [made available by Robert Gold Associate Director, Software and Embedded Systems, Office of the Deputy Under Secretary of Defense (Science and Technology)]. However, as this happens, the complexity explosion of the software component causes serious concerns for the final quality of the products and the productivity of the engineering teams. In transportation, the productivity of embedded software writers using the traditional methods of software development ranges in the few tens of lines per day. The reasons for such a low productivity are in the time needed for verification of the system and long redesign cycles that come from the need for developing full system prototypes for the lack of appropriate virtual engineering methods and tools for embedded software. Embedded software is substantially different from traditional software for commercial and corporate applications. By virtue of being embedded in a surrounding system, the software must be able to continuously react to stimuli in the desired way, i.e., within bounds on timing, power consumed, and cost. Verifying the correctness of the system requires that the model of the software be transformed to include information that involves physical quantities to retain only what is relevant to the task at hand. In traditional software systems, the abstraction process leaves out all the physical aspects of the systems as only the functional aspects of the code matter.

Given the impact that embedded software has on the safety of embedded system devices and on the quality of the final artifact, there is an increasingly strong interest in having high assurance that embedded software is correct. Software certification demonstrates the reliability and safety of software systems in such a way that it can be checked by an independent authority with minimal trust in the techniques and tools used in the certification process itself. It builds on existing software assurance, validation, and verification techniques but introduces the notion of explicit software certificates, which contain all the information necessary for an independent assessment of the properties. Software certification has been required by military applications for years and has been recently extended to the U.S. aviation sector. The FAA accepted the DO-178B regulations as the means of certifying all new aviation software. A joint committee with the European authorities has been recently empowered to "promote safe implementation of aeronautical software, to provide clear and consistent ties with the systems and safety processes, to address emerging software trends and technologies, and to implement an approach that can change with the technology" [69], [70]. I believe that certification will expand into new safety-critical domains and will create an additional, serious burden on the embedded software design process not only for the aviation industry but for an increasingly large number of companies worldwide. Note that today, the main scope of the certification process relates to the process followed to develop software. I believe it will be of extreme importance to link the certification process with the content of the software and not only with the development process. This approach will have to include formal verification techniques as I believe this is the only way to increase the confidence in the correctness of the software.

3) Integration Complexity: A standard technique to deal with complexity is decomposing "top-down" the system into subsystems. This approach, which has been customarily adopted by the semiconductor industry for years, has a limitation as a designer or a group of designers has to fully comprehend the entire system and to partition appropriately its various parts, a difficult task given the enormous complexity of today's systems. Hence, the future is one of developing systems by composing pieces that all or in part have already been predesigned or designed independently by other design groups or even companies. This has been done routinely in vertical design chains for example in the avionics and automotive verticals, albeit in a heuristic and ad hoc way. The resulting lack of an overall understanding of the interplay of the subsystems and of the difficulties encountered in integrating very complex parts causes system integration to become a nightmare in the system industry. For example, Jurgen Hubbert, then in charge of the Mercedes-Benz passenger car division, publicly stated in 2003: "The industry is fighting to solve

problems that are coming from electronics. Companies that introduce new technologies face additional risks. We have experienced blackouts on our cockpit management and navigation command system and there have been problems with telephone connections and seat heating."

I believe that in today's environment this state is the rule rather than the exception for the leading system original equipment manufacturers (OEMs)<sup>1</sup> in all industrial sectors [51]. The source of these problems is clearly the increased complexity but also the difficulty of the OEMs in managing the integration and maintenance process with subsystems that come from different suppliers who use different design methods, different software architecture, different hardware platforms, and different (and often proprietary) real-time operating systems. Therefore, there is a need for standards in the software and hardware domains that will allow plug-and-play of subsystems and their implementation. The ability to integrate subsystems will then become a commodity item, available to all OEMs. The competitive advantage of an OEM will increasingly reside on novel and compelling functionalities.

There is also the need for improving the interaction among all the players in the supply chain to improve the integration challenges in a substantial way as I argue in the next section.

## B. Industrial Supply Chain Landscape

The design and supply chains are the backbone for any industrial sector. Their health and efficiency are essential for economic viability. While tools for supply chain management have been around for quite some time, support for the design chain has not been pursued nearly as vigorously. There are great opportunities for improving the situation substantially at least in the safety-driven industrial sector, which includes the transportation as well as industrial automation domain, with a combination of tools and methodologies. We are just at the beginning.

Integration of electronic and mechanical design tools and frameworks will be essential in the near future. Integration of chemical, electronic, and biology tools will also be essential in the further future for nanosystems. Data integration and information flow among the companies forming the chain have to be supported. In other words, it is essential that the fundamental steps of system design (functional partitioning, allocation on computational resources, integration, and verification) be supported across the entire design development cycle. Thus, whether the integrations pertains to SW-SW integration on a distributed network, HW-SW integration on a single electronic control unit (ECU), or electronics and mechanical integration for a subsystem, tools and models have to

<sup>&</sup>lt;sup>1</sup>In this paper, OEM is used to refer to the companies that acquire a product or component and reuse or incorporate it into a new product with their own brand names. Examples are Mercedes, GM, and Toyota, as well as Boeing and Airbus.

be integrated seamlessly from a static point of view (e.g., data dictionaries and off-line model transformations) and dynamic point of view (e.g., cosimulation, HW-in-the-loop simulations and emulation).

Assuming the design methodology and the infrastructure for design chain integration are all in place, what will be the implication on the industrial structure?

The dynamics in the system industry is similar across the vertical domains but certainly there are important differences. For example, for embedded controllers in industrial engineering applications, automotive, avionics, energy production, and health related equipment, safety considerations, and hence hard real-time constraints, are of paramount importance. In the case of consumer electronics, including entertainment subsystems in cars and airplanes, cell phones, cameras, and games, the concerns are on sound, video, and recording quality and on the look and feel of the devices in presence of severe cost constraints. I will briefly discuss the cell phone design chain and the automotive design chain as the representatives of the embedded system market dynamics.

- 1) Mobile Communication Design Chain: The cell phone industrial segment is a complex ecosystem in continuous evolution with the following actors.

- a) Application developers such as gaming, ring tones, and video. These companies sell their products directly to the end customer except in cases where these applications come bundled either with standard services like voice offered by service providers such as Cingular, Verizon, or Telecom Italia, or with the device itself offered by makers such as Nokia, Motorola, Samsung, or Ericsson. Their designs are, in general, implemented in software running on the platform provided by the device manufacturers who choose also the OS.

- b) Service providers who offer the access to the network infrastructure for voice and data. These providers also offer other services such as news, weather information, and traffic. The GSM standard introduced (and mandated) the use of the subscriber identity module (SIM), a smart card that securely stores the key identifying a mobile phone service subscriber, as well as subscription information, saved telephone numbers, preferences, text messages, and other information. The use of the SIM card is important in the dynamics of the vertical segment as it is under control of the service providers. The service provider technology relates to the management of the infrastructure and of the service delivery. They worry, for example, about communication handoffs when cell boundaries are traversed and base-station location.

- c) *Device makers* who manufacture the mobile terminal, e.g., the cell phone. Device makers

- must master a number of different technologies as they manufacture systems with significant software content (more than 1 million lines of code today) and hardware content including computing and communication circuitry involving analog and RF. In most cases, the IC content is obtained by chip manufacturers such as Qualcomm, TI, Freescale, and ST, but it may also be designed by captive teams. One of the many challenges of a mobile terminal manufacturer is integrating heterogeneous semiconductors manufactured by different companies (for example, DSPs and microcontrollers for the digital part, base-band, and RF circuitry) whose interaction must be accurately predicted and controlled to provide the functionality with no errors. There is a significant IP content acquired by middleware software providers such as the Symbian OS, an operating system designed for mobile devices, with associated libraries, user interface frameworks, and reference implementations of common tools, produced by Symbian Ltd. In addition, styling, ergonomics, and user-friendliness are major attractions for the end customer.

- *IC providers* who offer semiconductors and other IPs that implement a variety of a mobile terminal functions. Semiconductor technology has had a major impact in the diffusion of mobile terminals as it is responsible for the dimension, power consumption, performance, functionality, and cost of the terminal. Because of the complexity of the design and of the need of interfacing with other vendors, IC manufacturers have turned to a particular design style that is the major content of this paper, platform-based design. The TI OMAP [55] platform together with the Nexperia Philips platform for digital video are the first examples of complex semiconductors designed in this style. Given the sale volumes of mobile terminals, IC manufacturers are competing fiercely and to provide the features needed by the device manufacturers, they had to enter into systemlevel design and into the development of significant software components including device drivers and other middleware. The semiconductor manufacturers are themselves integrating third party IPs.

- e) *IP providers* who provide components to the rest of the design chain. Symbian (with its OS for cell phones), Microsoft (with Windows CE), and ARM (with its processors) are examples of IP providers. These components are integrated in the semiconductors or in the terminal to perform an important function. They are instrumental to the functioning of the devices but cannot be sold to the end customer *per se*.

f) Outsourcing companies who provide design and manufacturing services to the rest of the chain. For example, Flextronics provides manufacturing services to a large variety of companies in the system domain including mobile terminal manufacturers. E-silicon [73] in U.S., Accent [6] in Europe and Faraday [87] in Taiwan offer design services to semiconductor and device manufacturers for part or entire chips as well as brokerage services to manage the interactions with silicon foundries. Finally, semiconductor foundries such as TSMC [200], IBM [153] and UMC [201] provide IC manufacturing services.

Today, there is a great deal of competition and turf battles to determine where the added value is inserted. For example, the boundary between service providers and device makers as well as the one between device and IC makers is under stress. Service providers favored the SIM card as a way of capturing value in their products and defend it against the device makers. The standard that limits the communication bandwidth between SIM cards and the cell phone electronics defends the device makers turf against the intrusion of the service providers. The device makers defend their added value against IC manufacturers by avoiding being locked into a single provider situation, farming out different components to different companies. In addition, they force, whenever possible, the IC providers to use standards that favor the possibility of using different IPs as they see fit. The use of the Open Core Protocol [157] standard in the TI OMAP [55] platform is a case where the interest of the device makers and the one of the IC provider aligned since it was also the interest of the IC provider to be able to incorporate quickly external and internal IPs. My opinion is that providing a unified methodology and framework, we will favor the balance of the chain where everyone reaches an equilibrium point that maximizes the welfare of the system.

- 2) Automotive Design Chain: The need for integrating widely different subsystems such as safety, propulsion, communication, and entertainment makes this vertical very interesting for our purposes. Today, the roles of car makers and their suppliers are relatively stable but they are undergoing a period of stress due to the increased importance of electronics and its added value. The Automotive supply chain includes:

- a) Car manufacturers (OEMs) such as GM, Ford, Daimler-Chrysler, and Toyota, who provide the final product to the consumer market.

- b) Tier 1 suppliers such as Bosch, Contiteves, Siemens, Nippon Denso, Delphi, and Magneti-Marelli, who provide subsystems such as powertrain management, suspension control, and brake-by-wire devices to OEMs.

- Tier 2 suppliers, e.g., chip manufacturers such as Freescale, Infineon, ST, and Renesas, IP providers

- e.g., ARM and RTOS suppliers such as WindRiver and ETAS, who serve OEMs and more likely Tier 1 suppliers.

- Manufacturing suppliers such as Flextronics and TSMC who provide manufacturing services. Opposite to verticals that are not safety critical, liability issues make the recourse to outside manufacturing not as common. However, there are signs that manufacturing for Tier 1 suppliers is increasingly considered for outsourcing.

Car makers express the desire of gaining a stronger grip on the integration process and on the critical parts of the electronics subsystems. At the same time, there is evidence that sharing IPs among car makers and Tier 1 suppliers could improve substantially time-to-market, development, and maintenance costs. The essential technical problem to solve for this vision is the establishment of standards for interoperability among IPs and tools. AUTOSAR [107], a world-wide consortium of almost all players in the automotive domain electronics supply chain, has this goal very clear in mind. However, there are technical and business challenges to overcome. In particular, from the technical point of view, while sharing algorithms and functional designs seems feasible at this time, the sharing of hard real-time software is difficult even assuming substantial improvements in design methods and technology, if run-time efficiency has to be retained. The issues are related to the interplay that different tasks can have at the RTOS level. The timing of the software tasks depend on the presence or absence of other tasks. A scheduling policy that could prevent timing variability in the presence of dynamical changing task characteristics can be conceived (for example, timing isolation or resource reservation policies) but it will carry overhead, albeit potentially not prohibitive; further, this kind of policy is not supported by any of the commercially available RTOS. This situation is the standard tradeoff between efficiency and reliability but it has more important business implications than usual. In fact, if software from different sources has to be integrated on a common hardware platform, in the absence of composition rules and formal verification of the properties of composed systems, who will be responsible for the correct functioning of the final product?

Whoever will take on this responsibility would need a very strong methodology and an iron fist to make suppliers and partners comply with it. This may not be enough, in the sense that software characteristics are hard to pin down and with the best intentions of this world, one may not be able to guarantee functional and timing behavior in the presence of foreign components. The constant growth of complexity of the embedded systems designed today makes manual analysis and design impractical and error prone. The ideal approach would be a tool that could map automatically the set of tasks onto the platform guaranteeing the correct functionality and timing with optimal resource utilization [160]. This

tool should take the design description at the pure functional level with performance and other constraints and the architecture of the platform and produce correct settings for the RTOS and optimized code. We are still far from this ideal situation. It is likely, then, that the responsibility for subsystem integration will still rest with the car manufacturers but the responsibility for integrating software components onto ECUs will be assigned to Tier 1 suppliers. In this case, the burden of Tier 1 suppliers will be increased at a possibly reduced premium because of the perceived reduction in added value. This is likely to be an unstable model and major attention should be devoted to find a common ground where both car makers and suppliers find their economic return.

If the strategy followed by car makers in AUTOSAR succeeds, then it is likely that a global restructuring of the industry will take place by creating an environment where Tier 1 players with small market share will find themselves in a difficult position unless they find a way of competing on a more leveled ground with the major stake holders. In this scenario, Tier 2 suppliers including IP providers may find themselves in a better position to entertain business relations directly with the car manufacturer. Tool providers will be in a more strategic position as providers of mapping tools that make the business model feasible. Hence, it is likely that a shift of recognized value will take place from Tier 1 suppliers towards tool providers and Tier 2 suppliers. The redistribution of wealth in the design chain may or may not be a positive outcome for the health of the industrial sector. If the discontinuities are sharp, then there may be a period of instability where much effort will be required to keep the products coming out with quality and reliability problems that may be larger than the ones observed lately. However, if it is well managed, then a natural shake-up with stronger players emerging will have a double positive: more quality in the products at lower cost. An additional benefit from a real plug-and-play environment will be the acceleration of the rate of innovation. Today, the automotive sector is considered conservative and the innovations in design methods and electronic components are slow to come. For example, if a well-oiled mechanism existed to migrate from one hardware platform to another, the "optimal" solutions would be selected instead of the ones that have been traditionally used. In this case, the Tier 2 market place will also be rationalized and the rate of innovation will likely be increased.

As a final consequence, the introduction of new functionalities will be a matter of algorithm and architecture rather than detailed software and hardware selection. The trend in electronics for the automotive industry (but for other verticals as well) is clear: less customization, more standardization. For a subsystem supplier, the choice will be richer in terms of platforms but it will not require heavy investment in IC design or RTOS development. For car manufacturers, the granularity of the choices will be

also richer because of interoperability. They will have the choice of selecting entire macro systems or components that could be integrated in a large automotive platform. The choice will be guided by cost, quality, and product innovation.

The final goal of the strategy is rather clear. The way of getting there is not as clear and the road has many bumps and turns that are difficult to negotiate. A positive outcome will have to come from a process of deep business and technical cooperation among all players in the design chain as well as the research community. It is a unique opportunity and a great challenge.

3) Remarks on the Needs of the Supply Chains: The design chains should connect seamlessly to minimize design errors and time-to-market delays. Yet, the boundaries among companies are often not as clean as needed and design specs move from one company to the next in nonexecutable and often imprecise forms, thus yielding misinterpretations and consequent design errors. In addition, errors are often caught only at the final integration step as the specifications were not complete and imprecise; further, nonfunctional specifications (e.g., timing, power consumption, size) are difficult to trace. I believe also that since the design process is fragmented, product optimization is rarely carried out across more than one company boundary. If the design process were carried out as in a unique "virtual" company including all the players shown above, the overall ecosystem would greatly benefit. We have seen that many of the design chain problems are typical of two very diverse verticals, the difference between the two being in the importance given to time-to-market and to the customer appeal of the products versus safety and hard-time constraints. Similar considerations could be drawn also for the consumer electronic market at large that shares many of its characteristics with the wireless communication market. This consideration motivates the view that the unified methodology and framework could be used in several (if not all) industrial vertical domains.

# III. PRINCIPLES OF A UNIFIED DESIGN APPROACH: PBD

As I will discuss in Section V, most of the present approaches to SLD used in industry have the drawback of primarily addressing either hardware or software but not both. Hardware/software codesign has been a topic of interest for years, but the proposed methodologies have still treated the two aspects essentially in a segregated way. Software approaches miss time and concurrency in their semantics making it pretty much impossible to describe, synthesize, and verify hardware. Hardware approaches are too specific to the hardware semantics to work well for software designers. I also believe that the levels of abstraction available in these approaches are not rich

enough to allow the supply chain to exchange design data in a seamless fashion.

These drawbacks cause the presently available approaches to address some of the challenges presented in Section II but not all, failing especially in the integration complexity realm and in the supply chain support domain. A more powerful approach would be to use an allencompassing methodology and the supporting tools that:

- would include both hardware and embeddedsoftware design as two faces of the same coin;

- favor the use of high levels of abstraction for the initial design description;

- offer effective architectural design exploration;

- achieve detailed implementation by synthesis or manual refinement.

In this section I present the PBD methodology and argue that it meets these requirements.

The concept of "platform" has been around for years. The main idea of a platform is one of reuse and of facilitating the work of adapting a common design to a variety of different applications. Several papers and books have appeared in the literature discussing platforms and their use in embedded system design (see for example, [48], [95], [129], [170], [171], [173], [175], and [176].

In this section, I first introduce the use of the platform concept in industry, then I present a distilled way of considering platforms as the building blocks for a general design methodology that could be used across different boundaries. I then present the application of this methodology to an emerging system domain application, wireless sensor networks, to illustrate the unification power of platform-based design.

## A. Conventional Use of the Platform Concept

There are many definitions of "platform" that depend on the domain of application.

IC Domain: a platform is considered a flexible integrated circuit where customization for a particular application is achieved by programming one or more of the components of the chip. Programming may imply metal customization (gate arrays), electrical modification (FPGA personalization), or software to run on a microprocessor or a DSP. For example, a platform may be based on a fixed micro-architecture to minimize mask-making costs but flexible enough to warrant its use for a set of applications so that production volume will be high over an extended chip lifetime. Microcontrollers designed for automotive applications such as the Freescale PowerPC are examples of this approach. The problem with this approach is the potential lack of optimization that in some applications may make performance too low and size too large.

An extension of this concept is a "family" of similar chips that differ for one or more components but that are based on the same microprocessor(s). Freescale developed the Oak Family [92] of PowerPC-based microcontrollers that cover the market more efficiently by differing in flash

memory size and peripherals. The TI OMAP platform [55] for wireless communication<sup>2</sup> was indeed developed with the platform concept well in mind. J.-M. Chateau of ST Microelectronics commenting on its division commitment to platform-based design defines it "as the creation of a stable microprocessor-based architecture that can be rapidly extended, customized for a range of applications, and delivered to customers for quick deployment."

The use of the platform-based design concept actually started with the Phillips Nexperia Digital Video Platform (DVP). The concept of PBD for IC design has not been without its critics. G. Smith, the former Gartner Data Quest Analyst for CAD, pointed out a number of shortcomings [185] that make, in his words, PBD work well in an embedded software development context as advocated in [176] but not so for chip design. However, not a month later, in an interview [62], [213], McGregor, former CEO of Philips semiconductors was quoted: "... we redoubled the company's efforts in platform-based design. Philips embraced the idea early-in the mid'90s, The recommitment to the platform approach under my watch is among my most notable accomplishments." In another important quote: "ST's Geyres attributed ST's continued success in the set-top business to its migration from systems-on-chip to application platforms," [214]. At this time, there is little doubt that PBD has made significant inroads in any semiconductor application domain. The Xilinx Virtex II [210] family is a platform rich in flexibility offered by an extensive FPGA fabric coupled with hard software programmable IPs (up to four PowerPC cores and a variety of peripherals. The FPGA fabric is enriched by a set of "soft" library elements such as the microblaze processor and a variety of smaller granularity functional blocks such as adders and multipliers.

I believe there will be a converging path towards the platform of the future, where traditional semiconductor companies will increase the flexibility of their platforms by possibly adding FPGA-like blocks and heterogeneous programmable processors, while the FPGA-based companies will make their platforms more cost and performance efficient by adding hard macros, thus differentiating their offerings according to the markets of interest. The more heterogeneity is added to the platform, the more potential for optimizing an application at the price of a more complex design process for the application engineers who have to allocate functionality to the various components and develop code for the programmable parts. In this context, the interaction among the various components has problems similar to those faced by the system

<sup>&</sup>lt;sup>2</sup>From the TI home page: "TI's OMAP Platform is comprised of market proven, high-performance, power efficient processors, a robust software infrastructure and comprehensive support network for the rapid development of differentiated internet appliances, 2.5G and 3G wireless handsets and PDAs, portable data terminals and other multimedia-enhanced

companies in an inherently distributed implementation domain (e.g., cars, airplanes, industrial plants). The "right" balance among the various components is difficult to strike and the methodology I will describe later is an attempt to give the appropriate weapons to fight this battle.

PC Domain: PC makers and application software designers have been able to develop their products quickly and efficiently around a standard "platform" that emerged over the years. The "architecture" platform standards can be summarized in the following list.

- The x86 instruction set architecture (ISA) makes it possible to reuse the operating system and the software application at the binary level3.

- 2) A fully specified set of busses (ISA, USB, PCI) make it possible to use the same expansion boards or IC's for different products.

- A full specification of a set of I/O devices, such as keyboard, mouse, audio and video devices.

All PCs should satisfy this set of constraints. Both the application developers and the hardware designers benefited from the existence of a standard layer of abstraction. Software designers have long used welldefined interfaces that are largely independent from the details of the hardware architecture. IC designers could invent new micro-architectures and circuits as long as their designs satisfied the standard. If we examine carefully the structure of a PC platform, we note that it is not the detailed hardware micro-architecture that is standardized, but rather an abstraction characterized by a set of constraints on the architecture. The platform is an abstraction of a "family" of micro-architectures. In this case, IC design time is certainly minimized since the essential components of the architecture are fixed and the remaining degrees of freedom allow some optimization of performance and cost. Software can also be developed independently of the new hardware availability, thus offering a real hardware-software codesign approach.

System Domain: The definition of a platform is very loose. This quote from an Ericsson press release is a good example: "Ericsson's Internet Services Platform is a new tool for helping CDMA operators and service providers deploy Mobile Internet applications rapidly, efficiently and cost-effectively." The essential concept outlined here is the aspect of the capabilities a platform offers to develop quickly new applications. It is similar to the application software view of a PC platform, but it is clearly at a higher level of abstraction. The term platform has been also used by car makers to indicate the common features shared between different models. For automobiles, platforms are characterized by common mechanical features such as engines, chassis, and entire powertrains. It is not infrequent to see a number of different models even across brands share many mechanical parts, addressing different markets with optimized interior and styling. Here, the focus on subsystem commonality allows for faster time-to-market and less expensive development.

There are clearly common elements in the platform approaches across industrial domains. To make platforms a general framework for system design, a distillation of the principles is needed so that a rigorous methodology can be developed and profitably used across different design domains.

## B. Platform-Based Design Methodology

The principles at the basis of platform-based design consist of starting at the highest level of abstraction, hiding unnecessary details of an implementation, summarizing the important parameters of the implementation in an abstract model, limiting the design space exploration to a set of available components, and carrying out the design as a sequence of "refinement" steps that go from the initial specification towards the final implementation using platforms at various level of abstraction [44], [129], [174].

1) Platform Definition: A platform is defined to be a library of components that can be assembled to generate a design at that level of abstraction.

This library not only contains computational blocks that carry out the appropriate computation but also communication components that are used to interconnect the computational components.

It is important to keep communication and computation elements well separated as we may want to use different methods for representing and refining these blocks. For example, communication plays a fundamental role in determining the properties of models of computation. In addition, designing by aggregation of components requires a great care in defining the communication mechanisms as they may help or hurt design reuse. In design methodologies based on IP assembly, communication is the most important aspect. Unexpected behavior of the composition is often due to negligence in defining the interfaces and the communication among the components.

Each element of the library has a characterization in terms of performance parameters together with the functionality it can support.

The library is in some sense a parameterization of the space of possible solutions. Not all elements in the library are pre-existing components. Some may be "place holders" to indicate the flexibility of "customizing," a part of the design that is offered to the designer. For example, in a Virtex II platform, part of the design may be mapped to a set of virtual gates using logic synthesis and place-androute tools. For this part, we do not have a complete characterization of the element since its performance parameters depend upon a lower level of abstraction.

A platform instance is a set of components that is selected from the library (the platform) and whose parameters are set. In the case of a virtual component, the parameters are set by the requirements rather than by the implementation. In this case, they have to be considered as constraints for the next level of refinement.

This concept of platform encapsulates the notion of reuse as a family of solutions that share a set of common features (the elements of the platform). Since we associate the notion of platform to a set of potential solutions to a design problem, we need to capture the process of mapping a functionality (what the system is supposed to do) with the platform elements that will be used to build a platform instance or an "architecture" (how the system does what is supposed to do). This process is the essential step for refinement and provides a mechanism to proceed towards implementation in a structured way.

I strongly believe that function and architecture should be kept separate as functionality and architectures are often defined independently, by different groups (e.g., video encoding and decoding experts versus hardware/ software designers in multimedia applications). Too often I have seen designs being difficult to understand and to debug because the two aspects are intermingled at the design capture stage. If the functional aspects are indistinguishable from the implementation aspects, then it is very difficult to evolve the design over multiple hardware generations.

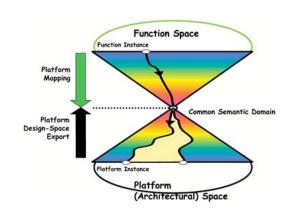

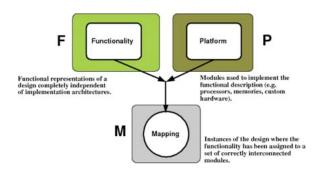

- 2) Design Process: The PBD design process is not a fully top-down nor a fully bottom-up approach in the traditional sense; rather, it is a meet-in-the-middle process (see Fig. 2) as it can be seen as the combination of two efforts.

- Top-down: Map an instance of the functionality of the design into an instance of the platform and propagate constraints.

- Bottom-up: Build a platform by choosing the components of the library that characterizes it and an associated performance abstraction (e.g., timing of the execution of the instruction set for a processor, power consumed in performing an atomic action, number of literals for technology independent optimization at the logic synthesis level, area and propagation delay for a cell in a standard cell library).

Fig. 2. PBD triangles.

Fig. 3. PBD process.

The "middle" is where functionality meets the platform. Given the original semantic difference between the two, the meeting place must be described with a common semantic domain so that the "mapping" of functionality to elements of the platform to yield an implementation can be formalized and automated.

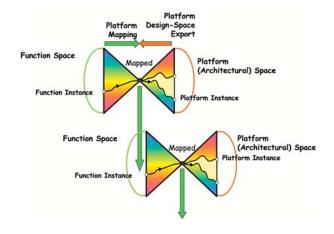

To represent better the refinement process and to stress that platforms may pre-exist the functionality of the system to be designed, we turn the triangles on the side and represent the "middle" as the mapped functionality. Then, the refinement process takes place on the mapped functionality that becomes the "function" at the lower level of the refinement. Another platform is then considered side-by-side with the mapped instance and the process is iterated until all the components are implemented in their final form. This process is applied at all levels of abstraction, thus exposing what I call the "fractal nature of design." Note that some of the components may have reached their final implementation early in the refinement stage if these elements are fully detailed in the platform.

The resulting Fig. 3 exemplifies this aspect of the methodology. It is reminiscent of the Y-chart of Gajski, albeit it has a different meaning since for us architecture and functionality are peers and architecture is not necessarily derived from functionality but may exist independently.3 It was used as the basis for the development of Polis [17] and of VCC [123]. The concept of architecture is well captured by the platform concept presented above.

The result of the mapping process from functionality to architecture can be interpreted as functionality at a lower level of abstraction where a new set of components, interconnects, and composition rules are identified. To progress in the design, we have to map the new

<sup>&</sup>lt;sup>3</sup>This diagram together with its associated design methodology was presented independently by Bart Kienhuis and colleagues (see e.g., [130]).

functionality to the new set of architectural components. In case, the previous step used an architectural component that was fully instantiated, then that part of the design is considered concluded and the mapping process involves only the parts that have not been fully specified as yet.

While it is rather easy to grasp the notion of a programmable hardware platform, the concept is completely general and should be exploited through the entire design flow to solve the design problem. For example, the functional side of Fig. 3 can be as high level as a denotational specification (find x such that f(x) = 0) and the corresponding platform can be a set of algorithms for operationalizing the specification (e.g., a Newton-Raphson algorithm and a nonlinear successive over relaxation scheme) together with their performance (e.g., quadratic or linear convergence). The choice of a platform instance would be in this case the selection of the algorithm to use together with the constraints that this choice requires (e.g., differentiability of f, nonsingularity of the Jacobian at the solution for Newton-Raphson). Assuming Newton-Raphson to be the choice, then this platform instance becomes the functional specification for the next layer. In this case, a library of linear equation solvers to be used in the Newton-Raphson algorithm is then the next layer platform. We can continue along this line of reasoning until we decide to use a particular computing platform for the implementation of the fully specified algorithm that is available.

3) Considerations on Use of PBD: In PBD, the partitioning of the design into hardware and software is not the essence of system design as many think, rather it is a consequence of decisions taken at a higher level of abstraction. Critical decisions are about the architecture of the system, e.g., processors, buses, hardware accelerators, and memories, that will carry on the computation and communication tasks associated with the overall specification of the design.

In the PBD refinement-based design process, platforms should be defined to eliminate large loop iterations for affordable designs. They should restrict the design space via new forms of regularity and structure that surrender some design potential for lower cost and first-pass success. The library of functional and communication components is the design space that we are allowed to explore at the appropriate level of abstraction.

Establishing the number, location, and components of intermediate "platforms" is the essence of PBD. In fact, designs with different requirements and specifications may use different intermediate platforms, hence different layers of regularity and design-space constraints. The tradeoffs involved in the selection of the number and characteristics of platforms relate to the size of the design space to be explored and the accuracy of the estimation of the characteristics of the solution adopted. Naturally, the larger the step across platforms, the more difficult is

predicting performance, optimizing at the higher levels of abstraction, and providing a tight lower bound. In fact, the design space for this approach may actually be smaller than the one obtained with smaller steps because it becomes harder to explore meaningful design alternatives and the restriction on search impedes complete design-space exploration. Ultimately, predictions/abstractions may be so inaccurate that design optimizations are misguided and the lower bounds are incorrect.

The identification of precisely defined layers where the mapping processes take place is an important design decision and should be agreed upon at the top design management level. Each layer supports a design stage where the performance indexes that characterize the architectural components provide an opaque abstraction of lower layers that allows accurate performance estimations used to guide the mapping process.

This approach results in better reuse, because it decouples independent aspects, that would otherwise be tied, e.g., a given functional specification to low-level implementation details, or to a specific communication paradigm, or to a scheduling algorithm. It is very important to define only as many aspects as needed at every level of abstraction, in the interest of flexibility and rapid design-space exploration.

# C. Application of PBD: Wireless Sensor Network Design

In this section, I demonstrate that PBD is applicable not only to digital designs and hardware/software codesign approaches (the most obvious applications) but also to design problems as different as wireless sensor networks. In these examples, I emphasize the levels of abstraction and their relative positions, as well as the way they relate to the overall design flow. I invite the interested readers to see [45], [61], and [168], for a set of different applications that include hardware/software co-design, analog design, automotive electronic system design, and communication design both on-chip and at the system level.

The application of Wireless Sensor Networks technology [54] to the design of field-area networks for industrial communication and control systems has the potential to provide major benefits in terms of flexible installation and maintenance of field devices, support for monitoring the operations of mobile robots, and reduction in costs and problems due to wire cabling [205], [217].

The software for control applications within industrial plants is usually written by process or mechanical engineers that are expert in process control technology, but know little of the communication and sensing infrastructure that has to be deployed to support these algorithms. On the other side, the communication infrastructure is designed by communication engineers that know little about process control technology. Moreover, the adoption of wireless technology further complicates the design of these networks. Being able to satisfy high requirements on communication performance over

an unreliable communication channel is a difficult task. Consequently, the gap between the control algorithm designers and the network designers will inevitably increase. This phenomenon might delay the adoption of wireless sensor networks technology.

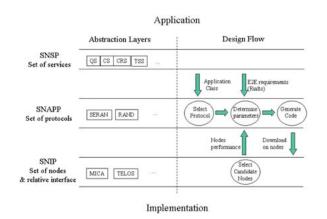

The platform-based methodology can contribute to the solution of these problems focusing the effort on the definition of a *clear set of abstraction layers* across which the design progresses. For a more detailed overview of the methodology, the interested readers is referred to [28]–[30] and [180]. The different abstraction layers presented below and their relationship are shown in Fig. 4.

The first layer is an application interface called sensor network service platform (SNSP). The SNSP defines a set of services available to the application engineer to specify the target application formally without dealing with the details of a particular network implementation. The SNSP offers a query service (QS) used by controllers to get information from other components, a command service (CS) used by controllers to set the state of other components, a timing/ synchronization service (TSS) used by components to agree on a common time, a location service (LS) used by components to learn their location, and a concept repository service (CRS) which maintains a map of the capabilities of the deployed system and it is used by all the components to maintain a common consistent definition of the concepts that they agreed upon during the network operation. While the SNSP description suffices to capture the interaction between controllers, sensors, and actuators, it is a purely functional description, which does not prescribe how and where each of these functions will be implemented. Hence, information such as communication protocols, energy, delay, cost, and memory size are not included.

The second abstraction layer is called *Sensor Network Ad hoc Protocol Platform (SNAPP)* [29]. The SNAPP defines a library of communication protocols and the interfaces that these protocols offer to the SNSP. In Fig. 4, RAND

Fig. 4. PBD for wireless sensor networks.

and SERAN are two examples of protocols that populate the SNAPP.

Once the communication protocol is selected, it must be implemented on a set of physical nodes. A description of the actual hardware platform is given by the sensor network implementation platform (SNIP) [180]. In Fig. 4, MICA [155] and TELOS [156] are two commonly available hardware platforms.

The process of mapping the SNSP description to a SNAPP instance and eventually to a SNIP instance goes through a set of steps. First, the selected topology and communication protocol must be ensured to be capable of supporting the sensing, actuation and communication requirements implied by the application.

Once the constraints on sensing, actuation, and communication have been derived, the methodology requires an abstraction of the physical layer properties of the proposed hardware platform (candidate SNIP instance) and selects an adequate topology and communication protocol among the ones available in the SNAPP. Finally, the parameters of the protocol are synthesized so that the given constraints are satisfied and energy consumption optimized.

Tools that help bridging between two different layers of abstraction have been developed for particular application domains [28].

Summarizing, the methodology:

- allows the control algorithm designer to specify the application using a clear interface that abstracts the drudgeries of the network implementation;

- derives a set of constraints on the end-to-end (E2E) latency and packet error rate that the network has to satisfy starting from the application description;

- derives a solution for MAC and Routing that satisfies requirements and optimizes for energy consumption using the E2E requirements and an abstraction of the hardware platform;

- 4) maps the communication protocol to the hardware nodes and the PLC.

The introduction of the levels of abstraction and of the tools allows a seamless path to implementation from highlevel application-driven specifications where various supply chain players can optimize their contributions. The layers of abstraction define the boundaries across which the design transition occurs. Note that application designers when using this approach can quickly adapt to a new implementation platform (even an heterogeneous one where different nodes may be provided by different vendors) exploiting the advantages of the technology without having to pay the price of redesigning their applications.

The definition of the platform levels allows us also to develop synthesis and verification tools that would have been impossible otherwise. This layered approach is

reminiscent of the standard ISO-OSI layering but it has important differences as the layers are not necessarily predefined and standardized and the potential of optimization is much greater. In some sense, PBD retains the favorable aspects of the layered approach to communication design while improving performance and design freedom.

# D. Platform-Based Design and Model-Driven Development

The paradigm that most closely resembles PBD is model-driven (software) development (MDD). MDD is a subject of intense research and investigation in the software development community as it bears much promise to improve the quality of software. For an excellent review of the state of the art and of challenges that MDD poses to the software community, I recommend the March 2006 issue of the IBM Systems Journal [66] and, in particular, the paper "Model-Driven Development: The good, the bad and the ugly" by B. Hailpern and P. Tarr, for a deep analysis of the pros and cons of the approach.

MDD is based on the concept of model-driven architecture. The OMG defines the term model-driven architecture (MDA) to be as follows: "MDA is based on a Platform-Independent Model (PIM) of the application or specification's business functionality and behavior. A complete MDA specification consists of a definitive platform-independent base model, plus one or more Platform-Specific Models (PSMs) and sets of interface definitions, each describing how the base model is implemented on a different middleware platform. A complete MDA application consists of a definitive PIM, plus one or more PSMs and complete implementations, one on each platform that the application developer decides to support. MDA begins with a model concerned with the (business-level) functionality of the system, independent of the underlying technologies (processors, protocols, etc.). MDA tools then support the mapping of the PIM to the PSMs as new technologies become available or implementation decisions change," [98].

The concept of separation of concerns between function and platform is clearly stated. The use of the mapping of functionality to platforms as a mean to move towards the final implementation is also expressed. However, the similarities between the two approaches end here as the definition of platform is not fully described nor are the semantics to be used for embedded software design.

The Vanderbilt University group [127] has evolved an embedded software design methodology and a set of tools based on MDD. In their approach, models explicitly represent the embedded software and the environment it operates in and capture the requirements and the design of the application, simultaneously. Models are descriptive, in the sense that they allow the formal analysis, verification, and validation of the embedded system at design time.

Models are also generative, in the sense that they carry enough information for automatically generating embedded software using the techniques of program generators. Because of the widely varying nature of embedded systems, the Vanderbilt researchers emphasize that a single modeling language may not be suitable for all domains; thus, modeling languages should be domain-specific (DSL). These languages have a significant impact on the design process [118] for complex software systems. In embedded systems, where computation and communication interact with the physical world, DSLs offer an effective way to structure information about the system to be designed along the "natural dimensions" of the application [86]. I take the position that DSLs for embedded systems should have a mathematically manipulable representation.

This view goes against the use of a general language for embedded systems and favors customization to obtain better optimization and easier adoption. However, customization carries obvious drawbacks in terms of development costs and support efforts. To decrease the cost of defining and integrating domain-specific modeling languages and corresponding analysis and synthesis tools, the model-integrated computing (MIC) [127] approach is applied in an architecture, where formal models of domain-specific modeling languages-called metamodels play a key role in customizing and connecting components of tool chains. The generic modeling environment (GME) [127] provides a framework for model transformations enabling easy exchange of models between tools and offers sophisticated ways to support syntactic (but not semantic) heterogeneity. The KerMeta metamodeling workbench [128], [159] is similar in scope.

In synthesis, MDD emphasizes design by (whenever possible automatic) model transformations. Model-based approaches have been applied for years in the hardware domain where one can argue that since the introduction of logic synthesis, this approach has had great success. Most of the formal approaches to hardware design are indeed model driven in the sense that a design model is successively transformed into hardware. In embedded software, the approach still has to be fully exploited as using a model-driven method requires the description of the software with mathematical models, a step that for most software designers is not easy. DSLs will probably help in pushing for the adoption of MDD in the embedded software community since it is possible to design these languages to meet the specific needs of a homogeneous group of designers thus allowing them to be more effective in expressing their designs. However, if indeed each design group is going to have its specific language, the problem will be how to interface the various parts of the design so that the composition can be analyzed and verified. I believe that this issue can be resolved only if the semantics of the languages are well understood and the interaction among parts described with different languages is mathematically well characterized. The Vanderbilt

group is addressing some of these issues with semantic anchoring of DSLs using abstract semantics based on abstract state machines [32], [103]. In addition, the MILAN framework [126] offers a number of simulation, analysis, and synthesis tools that leverage the MIC framework. A recent approach to "gluing" parts described by different languages consists of using higher level programming models and languages for distributed programming, called coordination models and languages [46], [50]. In the coordination model approach, one can build a complete programming model out of two separate pieces—the computation model and the coordination model. The computation model allows programmers to build a single computational activity, a single-threaded step-at-atime computation. The coordination model is the glue that binds separate activities into an ensemble. The similarity with the separation between computation and communication in PBD is strong.

A coordination language is "the linguistic embodiment of a coordination model" [46]. The most famous example of a coordination model is the Tuple Space in Linda, a language introduced in the mid 1980s, that was the first commercial product to implement a virtual shared memory (VSM), now popularly known as tuples-pace technology for supercomputers and large workstation clusters. It is used at hundreds of sites worldwide [16]. Linda can be seen as a sort of assembly level coordination language since it offers:

- very simple coordination entities, namely, active and passive tuples, which represent processes and messages, respectively;

- a unique coordination medium, the Tuple Space, in which all tuples reside;

- a small number of coordination laws embedded in four primitives only.

Coordination languages can be built on Linda to offer a higher level of abstraction construct to simplify the synchronization and message passing among the components. Many coordination languages have been built over the years. An excellent review of Linda derivatives and coordination languages such as Laura and Shade can be found in [161].

Once more, I advocate the add a strong mathematically sound semantics to the linguistic approach to composition. This is indeed the contribution of some of the environments for heterogeneous models of computation such as Ptolemy II and Metropolis.

#### E. Concluding Remarks on PBD

The notion of PBD presented in this section is being adopted rather widely by the EDA companies who are active in the system space or that are eyeing that market. CoWare [170] and Mentor Graphics [52] use platforms in their architectural design and design-space exploration tools pretty much in the sense I introduced here. Cadence and National Instruments use the concepts of platforms in

the description of their tools and approaches using diagrams similar to Fig. 2.

I believe PBD serves well the purpose of the supply chain as the layers of abstraction represented by the platforms can be used to define the hand-off points of complex designs. In addition, the performance and cost characteristics associated to the platforms represent a "contract" between two players of the design chain. If the platform has been fully specified with performance and cost given by the supplier, then the client can design at his/ her level of abstraction with the assumption that the "contract" will be satisfied [82], [134]. If the supplier has done his/her homework well, the design cycles are considerably shortened. If one or more of the components of the platform instance chosen by the client is not made available by the supplier, but it has to be designed anew, the performance assumed by the client can serve as a specification for the supplier. In both cases, the "contract" is expressed in executable form and prevents misunderstandings and long design cycles.

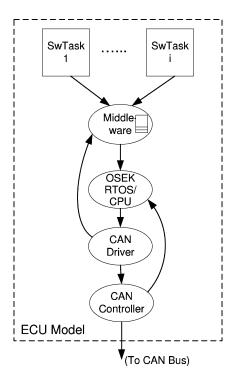

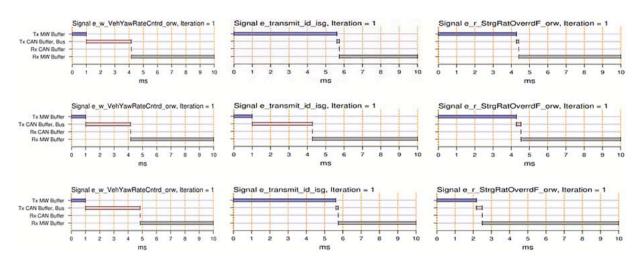

The platform concept is also ideal to raise the level of abstraction since it does not distinguish between hardware and software but between functionality and architecture. Hence, the design-space exploration can take place with a more degrees of freedom than in the traditional flows. In addition, the partitioning between hardware and software components can be done in an intelligent and optimized way.