News Story

Abshire part of CogniSense, a DARPA JUMP 2.0 center

Professor Pamela Abshire (ECE/ISR) is a co-PI in the new DARPA/SRC JUMP 2.0 Center, “CogniSense: The Center on Cognitive Multispectral Sensors,” one of seven JUMP 2.0 centers that have started operations in 2023. It is funded for five years. Professor Saibal Mukhopadhyay of the Georgia Institute of Technology is the principal investigator.

CogniSense brings together 20 researchers from 13 universities:

Mingoo Seok, Xiaofan Fred Jiang, Columbia University

Alyosha Christopher Molnar, Cornell University

Saibal Mukhopadhyay (PI), Justin Romberg, Muhannad Bakir, Georgia Institute of Technology

Cheng Huang, Iowa State University

Jelena Notaros, Massachusetts Institute of Technology

Vijay Raghunathan, Stanley Chan, Purdue University

Tingyi Gu, University of Delaware

Q. Jane Gu, University of California, Davis

James Buckwalter, Jonathan Klamkin, University of California, Santa Barbara

Amit Trivedi, Inna Partin Vaisband, University of Illinois, Chicago

Pamela Abshire, University of Maryland

Michael Flynn, David Blaauw, Hun Seok Kim, University of Michigan

About the DARPA JUMP program

The Defense Advanced Research Projects Agency (DARPA) is collaborating with the Semiconductor Research Corp. (SRC) and a consortium of defense and semiconductor companies to launch the second iteration of the Joint University Microelectronics Program (JUMP 2.0).

JUMP 2.0 builds off an earlier iteration of the SRC-led collaboration that was formed in 2018 to support university research centers focused on keeping the U.S. at the forefront of microelectronics innovation. It will pursue high-risk, high-payoff research spanning seven thematically structured centers. Each of seven university-led, multidisciplinary centers will focus on one overarching research theme identified as key to addressing emerging technical challenges. These defined interests, spurred by an increasingly connected world and a rapidly changing microelectronics landscape, will centralize long-term, pathfinding research aimed at breakthroughs applicable across defense and academia.

JUMP 2.0 seeks to significantly improve performance, efficiency, and capabilities across a range of electronics systems. Novel materials, devices, architectures, algorithms, designs, integration techniques, and other innovations are at the heart of problem-solving for next-generation information and communications challenges.

The centers will address the identified challenges, advance innovation and support and transition exploratory research to commercial and defense opportunities. The exploratory research will be supported with an eight- to twelve-year time horizon for transition to defense and commercial opportunities.

“We are at an inflection point in the evolution of computing systems and technologies,” said Roman Caudillo, Intel-SRC assignee and JUMP 2.0 Director. “The JUMP 2.0 program will be a key component in identifying and forging the best path forward by driving public-private investment for disruptive innovation in microelectronics systems at scale. I look forward to helping guide the semiconductor industry through the SRC JUMP 2.0 program and in cooperation with DARPA in the years to come.”

JUMP 2.0’s seven complementary systems (S) and technology (T) research themes, and the centers addressing each one are:

• Cognition (S): Next-generation AI systems and architectures. (COCOSYS: Center for the Co-Design of Cognitive Systems, Georgia Institute of Technology)

• Communications and Connectivity (S): Efficient communication technologies for ICT systems. (CUBIC: Center for Ubiquitous Connectivity, Columbia University)

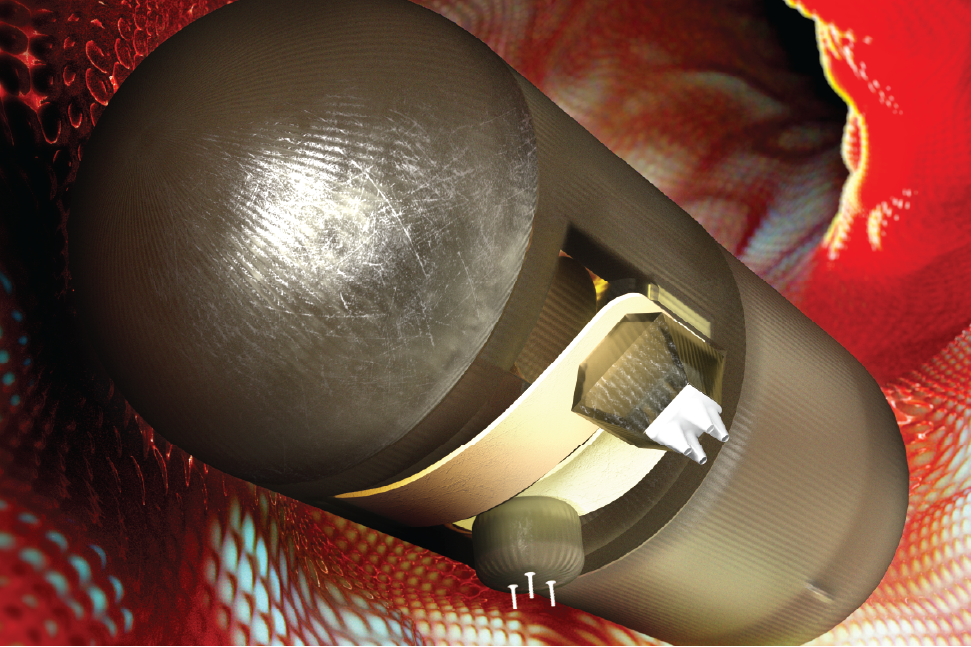

• Intelligent Sensing to Action (S): Sensing capabilities and embedded intelligence to enable fast and efficient generation of actions. (COGNISENSE: Center on Cognitive Multispectral Sensors, Georgia Institute of Technology)

• Systems and Architectures for Distributed Compute (S): Distributed computing systems and architectures in an energy efficient compute and accelerator fabric. (ACE: Evolvable Computing for Next Generation Distributed Computer Systems, University of Illinois Urbana-Champaign)

• Intelligent Memory and Storage (S): Emerging memory devices and storage arrays for intelligent memory systems. (PRISM: Center for Processing with Intelligent Storage and Memory, University of California San Diego)

• Advanced Monolithic and Heterogeneous Integration (T): Novel electric and photonic interconnect fabrics and advanced packaging. (CHIMES: Center for Heterogeneous Integration of Micro Electronic Systems, Penn State)

• High-performance Energy-Efficient Devices for Digital and Analog Applications (T): Novel materials, devices, and interconnect technologies to enable next-generation digital and analog applications. (SUPREME: Superior Energy-Efficient Materials and Devices, Cornell University)

Published January 12, 2023