News Story

Srivastava, Qu part of Department of Defense 'SHIP' Project hardware security team

Two University of Maryland hardware security experts are part of the large “State-of-the-Art Heterogeneous Integrated Packaging (SHIP) Prototype Project” funded by the Department of Defense (DoD) and led by Intel Corp.

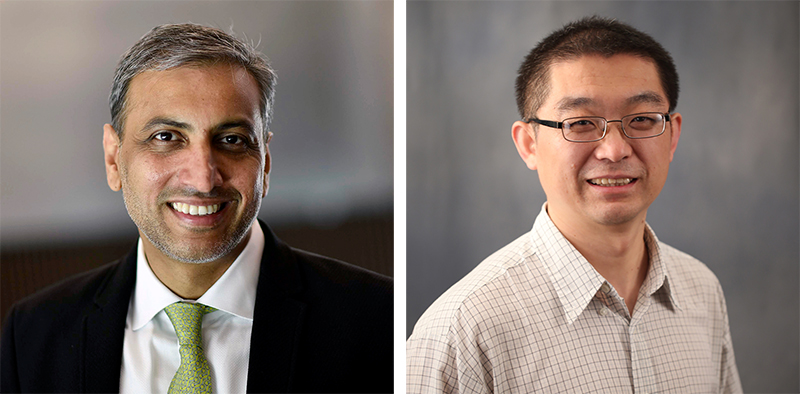

ISR Director and Professor Ankur Srivastava (ECE/ISR) is the principal investigator and Professor Gang Qu (ECE/ISR) is the co-PI for a three-year, $699,895 subcontract, “Red Team, Chiplet IP Protection and Countermeasures for State-of-the-Art Heterogeneous Integrated Packaging (SHIP) Prototype Project.”

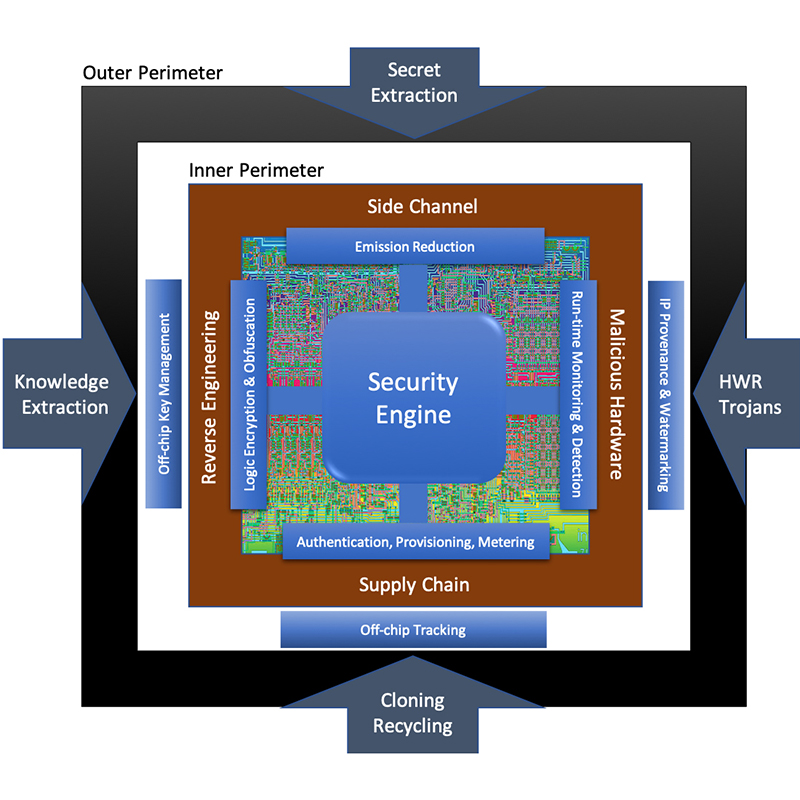

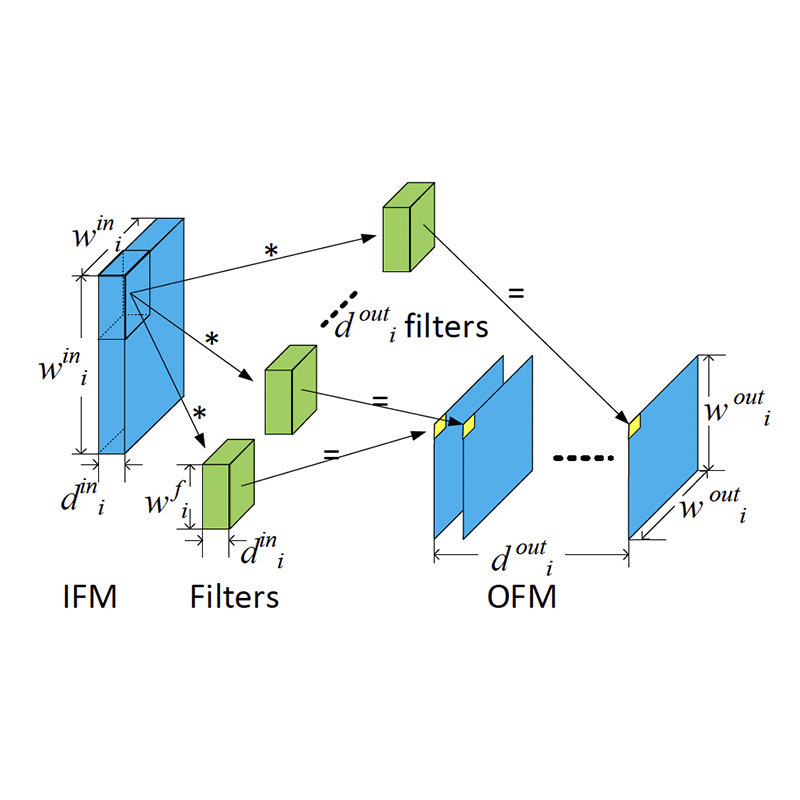

Their tasks will be to investigate a wide range of attack methodologies that could be used against protoype IC chiplets being developed in the SHIP project. The attacks include those framed in strong theoretical foundations such as SAT, appSAT and Bounded Model Checking, as well as those that rely on simulation and analysis. The researchers will explore FSM & Combinational Locking as well as Watermarking.

Srivastava will concentrate on theoretically rigorous attacks on obfuscation/locking: SAT and Bounded Model Checking. Using these attacks, he will attempt to find locking keys, both for FSM locking and combinational locking, that would make the locked netlist function properly.

He also will investigate practically useful attacks. For example, he will look at removal attacks on obfuscation, which seeks to remove the logic locking circuitry instead of finding the correct keys, including the signal probability skew (SPS)-based attack. He will also consider hill climbing attacks on obfuscation which search for the correct key using a hamming distance (HD)-guided hill climbing algorithm.

In addition, Srivastava also will attempt attacks that look for structural traces left by synthesis tools. These include machine learning-guided structural analysis attacks on hardware obfuscation, joint structural functional attacks on logic locking, and constant propagation attacks on logic locking.

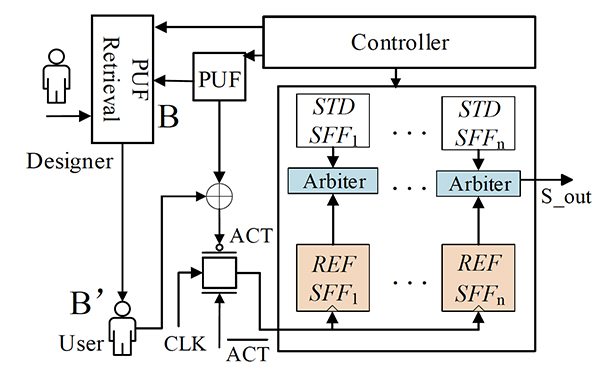

Qu will concentrate on assessing and improving the embedded digital watermarking technologies developed by SHIP that authenticate hardware IPs throughout their life cycle and perform provenance analysis. The main purpose of watermarking is to enable the IP designer or IP owner to identify and trace their IPs.

Qu and his team will first follow SHIP’s specification to identify the embedded watermark that authenticates hardware Ips. They will then apply attacking techniques such as random walk, scan chain side-channel, and machine learning to the finite state machine to reveal the embedded watermark and assess whether it actually is hard to detect. Then, for the same IP, Qu will design it twice, one without watermark and one without watermark. The performance of both designs will be compared to quantitatively compare the overhead introduced by watermark. For the sequential locking watermark scheme, Qu will report vulnerabilities found and develop attacks to tamper the watermark.

About the SHIP Project

SHIP is sponsored by the Office of the Under Secretary of Defense for Research and Engineering and funded by the Trusted and Assured Microelectronics program. Intel Federal LLC (Intel Corp.) is the prime contractor; the overall project principal research scientist is Intel’s David Kehlet.

The Navy desires to develop a secure, assessable, and cost effective way to design, manufacture, assemble and test in-package integration of system-critical components, such as digital (ASICs, Central Processing Units, FPGAs), analog, memory, mixed-signal, RF, and transceivers. DoD is also interested in creating a secure manufacturing flow to enable the rapid integration of microelectronics chips using heterogeneous integration allowing the acceleration of technology insertion through advanced prototyping.

The SHIP project will demonstrate a novel approach to integrated design, assembly, and testing that leverages the expertise of commercial industry. The prototype developed in the project also will incorporate heterogeneous packaging to allow the assembly of multiple, separately manufactured integrated circuit chips into a single package to increase performance, achieve less power consumption and latency, reduce size and improve reliability.

Currently, the program is developing prototypes of multichip packages and accelerating the advancement of interface standards, protocols and security. In this phase, Intel’s advanced heterogeneous packaging technologies are integral to the goal of making the latest military technology available in advanced system-level packaging.

SHIP prototypes will integrate special-purpose government chips with Intel’s advanced, commercially available silicon products, including field programmable gate arrays, application-specific integrated circuits and CPUs. This combination of technologies provides new paths for the U.S. government’s industry partners to develop and modernize the government’s mission-critical systems while taking advantage of Intel’s U.S. manufacturing capabilities.

Published December 1, 2020