News Story

Srivastava testing security of new delay locking technology

ISR Director and Professor Ankur Srivastava (ECE/ISR) is part of the Air Force Research Laboratory (AFRL) “Locked Electronics for Assured Design” (LEAD) program led by Northrop Grumman Corp.

He is the principal investigator for “Delay Locking ASIC IP Blocks to Protect Functionality,” a two-year, $200K subcontract.

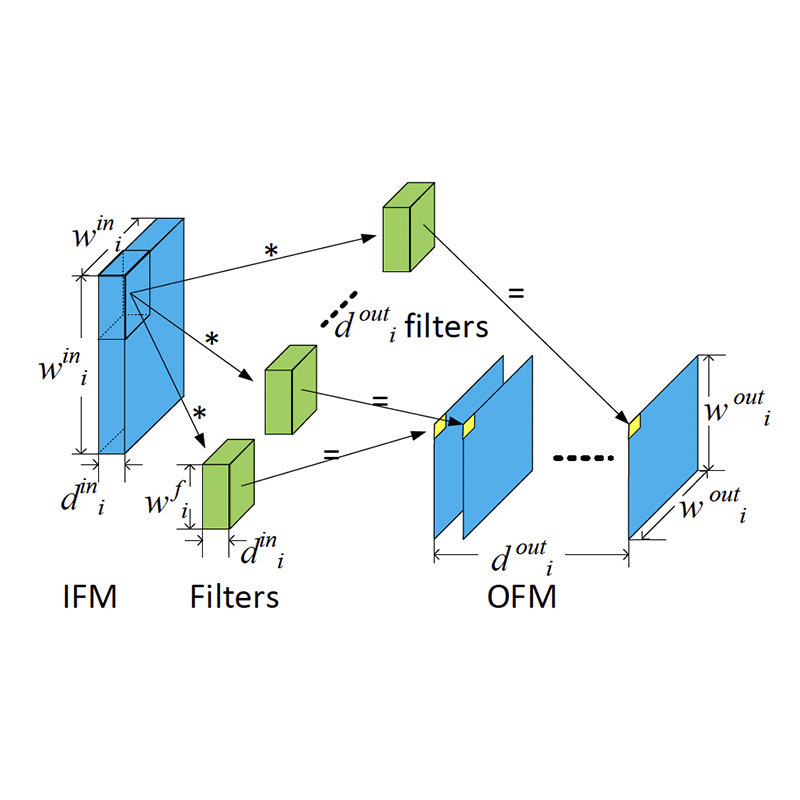

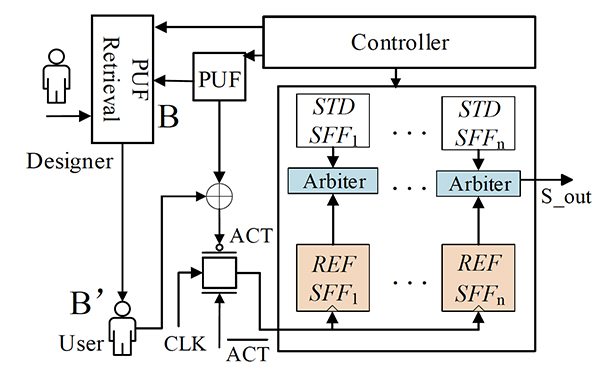

Logic locking is a technique that has been proposed to thwart IC counterfeiting and overproduction by an untrusted foundry. The security of logic locking has been threatened by the new “SAT” attack, which can effectively decipher the correct key of most logic locking techniques. In 2017, Srivastava and Yang Xie proposed a new technique called delay locking to enhance the security of existing logic locking techniques. In this technique, the key into a locked circuit not only determines its functionality, but also its timing profile. A functionality-correct but timing-incorrect key will result in timing violations, making the circuit malfunction.

In this new project, Srivastava’s team will employ rigorous mathematical techniques to quantitatively assess the performance of the time delay obfuscation technique in protecting ASIC chips. They also will evaluate the probability of reverse-engineering the key from the netlist, as well as the effectiveness of the method to prevent unauthorized use of the digital circuit. This analysis will lead to the development of associated tools and ultimately, new silicon tapeout with delay locking technology.

Published October 28, 2020